# Deliver your EBD model with confidence

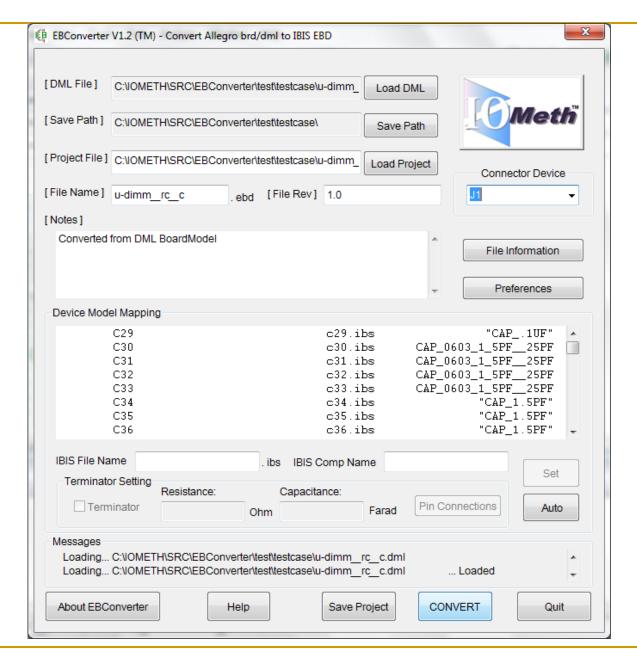

EBConverter V1.2™ Release 201104

### EBConverter V1.2 ™

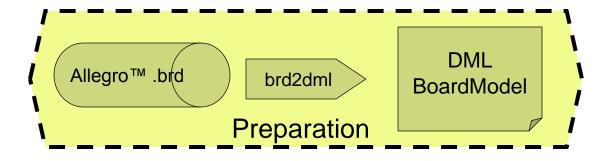

- Convert your Alllegro brd / dml to IBIS EBD model

Copyright © 2006-2011 IO Methodology Inc.

#### EBConverter V1.2™

- The most accurate IBIS EBD converter on the Market

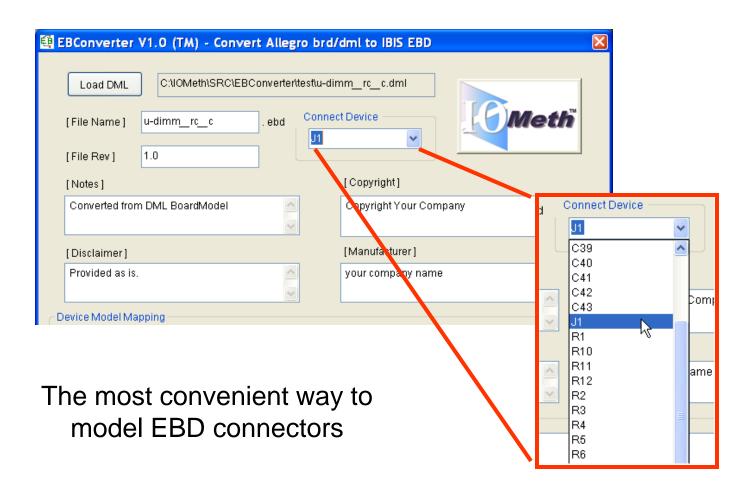

- Flexible Connect Device (Connector) selection

- Complete Connector Pin list

- Automatic serial/parallel terminator handling for complete extended netlist

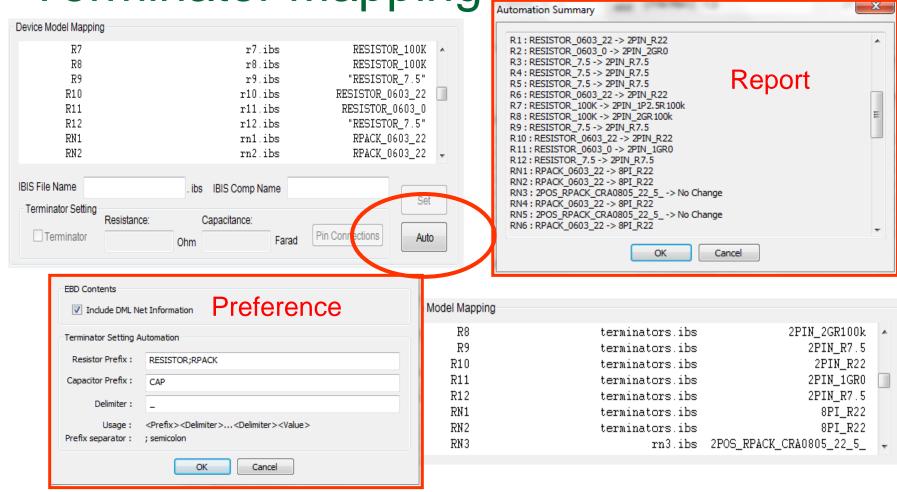

- Auto-mapping capability for terminator mapping

- Automatic embedded terminations in [Path Description] and IBIS Terminator model generations

- Keep all the data name (Net, RefDes, etc.) as the same as original board

- Optional remained DML boardmodel segment names as comments for easy verification

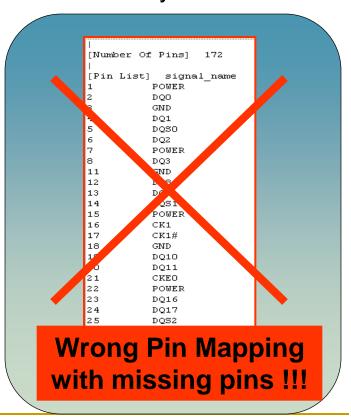

# Flexible Connect Device (Connector) Selection

Complete Connector Pin list

```

[Number Of Pins]

184

[Pin List] signal name

J1.1

POWER

J1.2

DQO

J1.3

GND

J1.173

J1.4

173

NC

DO1

| J1.174

J1.5

174

D060

DOSO

J1.175

J1.6

175

DQ61

DO2

| J1.176

J1.7

176

POWER

J1.17

J1.

177

DM7

8

J1/178

J1.9

DQ62

NC

J1.179

J1.10

179

DO63

10

NC

J1.180

| J1.11

180

POWER

GND

J1.181

| J1.12

181

SAO

12

DO8

J1.182

J1.13

182

SA1

13

D09

J1.183

J1.14

183

SA2

14

DQS1

| J1.184

J1.15

184

VDDSPD

15

POWER

```

#### Produced by another tool

#### Robust Terminator Handling

```

[Path Description] DQO

J1.2

Pin 2

| R@@X2130Yn370L1 @@J1.2

| ianored for

Embedded termination

|Len=0 L=0.000

XNTL XSTLX23

for extended netlist

Len=0.00382234

R@@X2350Y970 1 cc.wr

| ignored for Spice simulator

|Len=0 L=0.0000e+000 C=0.

e+000 R=1.0000e-006/

RN1.1 -> RN1.8 R=22

Len=0 R=22/

Net: DQOA

R@@X2350Y1370L1 @@RN1.8

ignored for Spice simulators

|Len=0 L=0.0000e+000 C=0.0000e+000 R=1.0000e-006/

XNTL XSTLX2350Y1370L1X4040Y5321L1

Len=0.0145933 L=3.6466e-007 C=8.8655e-011 R=4.5129e+000/

R@@X4040Y5321L1 @@U1.54

| ignored for Spice simulators

|Len=0 L=0.0000e+000 C=0.0000e+000 R=1.0000e-006/

Node U1.54

```

```

2PIN_2GR100K

[Component]

[Manufacturer] Created by EBConverter

max

[Comp|R pkg

NA

ManuL pkg

C pkg

「Pack

signal name

model name

R pkg

L pkg

term p0 g0 rp rg0

C_pkg [Series Pin Mapping]

pin 2

model name

series r100K c

[Pin]

signal

signal

term_p0_g0_rp_rg0

[Series Pin Mapping]

model name

series r0 c

[Model] term pO gO rp rgO

[Model] series r100K c

Model type Series

max

[Pullup Reference]

MΑ

[Pulldown Reference]

NA

[POWER Clamp Reference]

NA

[GND Clamp Reference]

| variable

[R Series]

100K

```

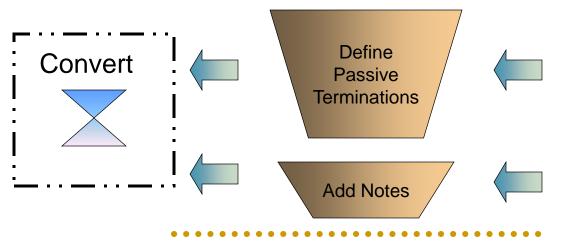

Auto-Mapping Capability for Terminator Mapping

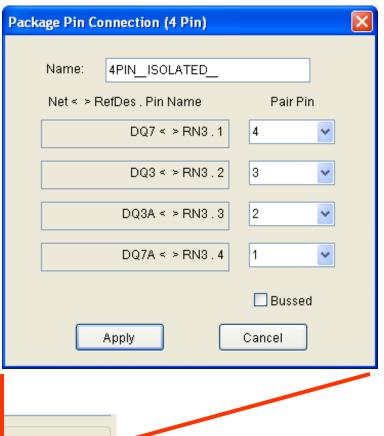

#### **Easy Terminator Work Wizard**

- Detect Net connections

- Handles Isolated and Bussed type resistor packs

- Automatic embedding solutions for extended nets

Terminator Setting

Resistance: Capacitance:

Terminator 22

Ohm

Farad

Pin Connections

#### Informational comments/notes

```

[Path Description] DQO

J1.2

Pin 2

| R@@X2130Yn370L1 @@J1.2

| ignored for Spice simulators

[Number Of Pins]

|Len=0 L=0.0000e+000 C=0.0000e+000 R=1.0000e-006/

XNTL XSTLX2350Y970L1X2130Yn370L1

[Pin List] signal name

Len=0.00382234 L=3.6466e-007 C=8.8655e-011 R=4.5129e+000/

J1.1

| R@@X2350Y970L1 @@RN1.1

J1.2

| ignored for Spice simulators

DOO

|Len=0 L=0.0000e+000 C=0.0000e+000 R=1.0000e-006/

| RN1.1 -> RN1.8 R=22

GND*

Len=0 R=22/

J1.4

| Net: DQOA

DO1

R@@X2350Y1370L1 @@RN1.8

J1.5

ignored for Spice simulators

DOSO

|Len=0 L=0.0000e+000 C=0.0000e+000 R=1.0000e-006/

J1.6

XNTL XSTLX2350Y1370L1X4040Y5321L1

DO2

J1.7

Len=0.0145933 L=3.6466e-007 C=8.8655e-011 R=4.5129e+000/

POWER

| R@@X4O4OY5321L1 @@U1.54

| ignored for Spice simulators

|Len=0 L=0.0000e+000 C=0.0000e+000 R=1.0000e-006/

Node U1.54

```

Keep the information as the original board Remain the segment info in EBD for easy verification

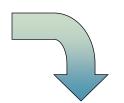

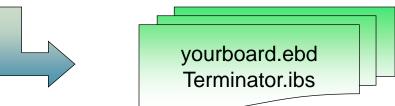

#### **Process Flow**

Load in EBC

## EBConverter V1.2 ™

- Convert your Alllegro brd / dml to IBIS EBD model